Today, a team led by Professor Ren Tianling from Tsinghua University made a breakthrough in the research of small-scale transistors, realizing the first transistor with sub-1nm gate length and good electrical properties.

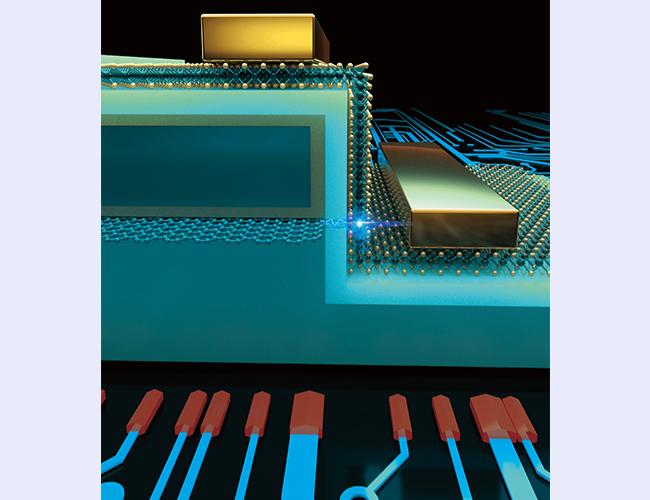

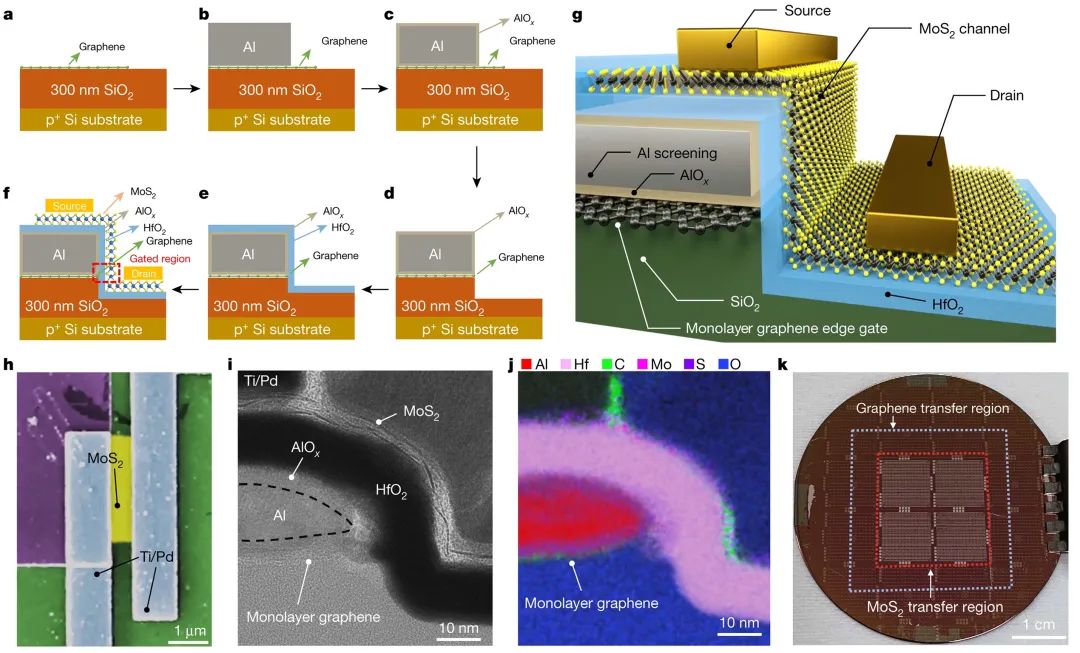

Schematic diagram of the sub-1 nanometer gate length transistor structure, the picture comes from Tsinghua University

Transistors are the core components of the chip, and the smaller gate size allows more transistors to be integrated on the chip and improves performance.

In 1965, Gordon Moore, one of the founders of Intel Corporation, proposed: "The number of transistors that can be accommodated on an integrated circuit chip doubles every 18-24 months, and the performance of microprocessors increases by one. times, or half the price." This is known as "Moore's Law" in the field of integrated circuits.

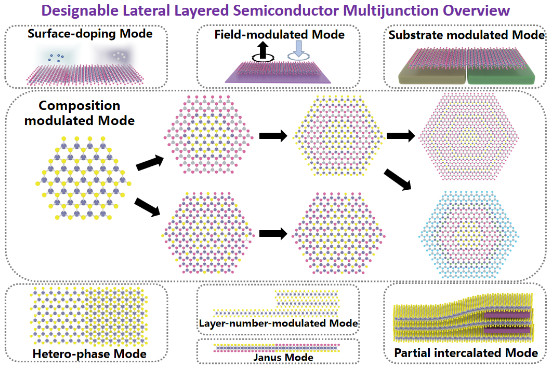

Over the past few decades, the gate size of transistors has been shrinking under the impetus of Moore's Law. However, in recent years, as the physical size of transistors has entered the nanoscale, short-channel effects such as reduced electron mobility, increased leakage current, and increased static power consumption have become more and more serious. Therefore, the development of new structures and new materials is imminent.

At present, the gate size of mainstream industrial transistors is more than 12 nanometers. How to promote the further miniaturization of the critical dimensions of transistors has attracted extensive attention from the academic community. In 2016, the Lawrence Berkeley National Laboratory and Stanford University reported in the journal Science that the team used metallic carbon nanotube materials and molybdenum disulfide (MoS2) to achieve a planar sulfide with a physical gate length of only 1 nanometer. Molybdenum transistor.

In order to further break through the bottleneck of transistors with gate lengths below 1 nanometer, Ren Tianling's team cleverly used the ultra-thin single-atom layer thickness and excellent conductivity of graphene films as gates to control the vertical molybdenum disulfide (MoS2) through the lateral electric field of graphene. ) channel switching, thereby achieving an equivalent physical gate length of 0.34 nm. The results were recently published online in the journal Nature.

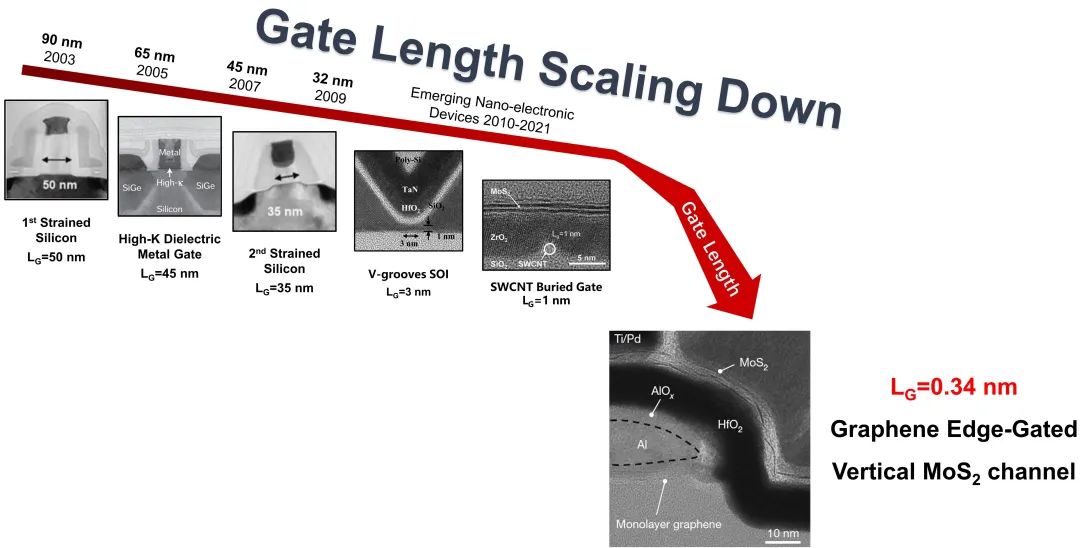

With the development of Moore's Law, the gate length of transistors is gradually shrinking, until this research achieves a transistor with a gate length of sub-1 nanometer. Picture from Tsinghua University

"We have achieved a transistor with the smallest gate length in the world," said Professor Ren Tianling from the School of Integrated Circuits at Tsinghua University. The study found that due to the single-layer two-dimensional molybdenum disulfide film, which has a larger effective electron mass and a lower dielectric constant than bulk silicon materials, transistors can be effectively controlled by an ultra-narrow sub-1nm physical gate length. The results of large and multiple sets of experimental test data also verify the large-scale application potential of this structure.

The simulation results based on process computer-aided design (TCAD) further demonstrate the effective regulation of the vertical molybdenum disulfide channel by the graphene fringe electric field, and predict the electrical performance of the transistor under the condition of shortening the channel length at the same time. This research work promotes the further development of Moore's Law to the sub-1 nanometer level, and provides a reference for the application of two-dimensional thin films in future integrated circuits.

Sub-1 nanometer gate length transistor device process flow diagram, characterization diagram and physical diagram, the picture comes from Tsinghua University

"It is very difficult to break this record for a long time," commented Huamin Li, a nanoelectronics scientist at the State University of New York at Buffalo. This new work further narrows the size limit of the gate to " the thickness of only one layer of carbon atoms".

The corresponding authors of the paper are Professor Ren Tianling and Associate Professor Tian He from the School of Integrated Circuits, Tsinghua University. Tsinghua University doctoral students Wu Fan and Shenyang and Associate Professor Tian He are the co-first authors. Other authors participating in the research include Tsinghua University master students Hou Zhan, Ren Jie, and doctoral students Gou Guangyang, Associate Professor Yang Yi and Associate Professor Sun Yabin, School of Communication and Electronic Engineering, East China Normal University

China

China English

English